# EXHIBIT I

# U.S. Patent No. 6,797,572 TSMC Products (TSMC 20nm and 28nm HKMG integrated circuit)

#### Case 1:19-cv-00308-MN Document 1.8, Filed 97/12/19 Page 3 of 26 PageID #: 159

"1. A method for forming a field effect transistor over a substrate, said method comprising steps of:"

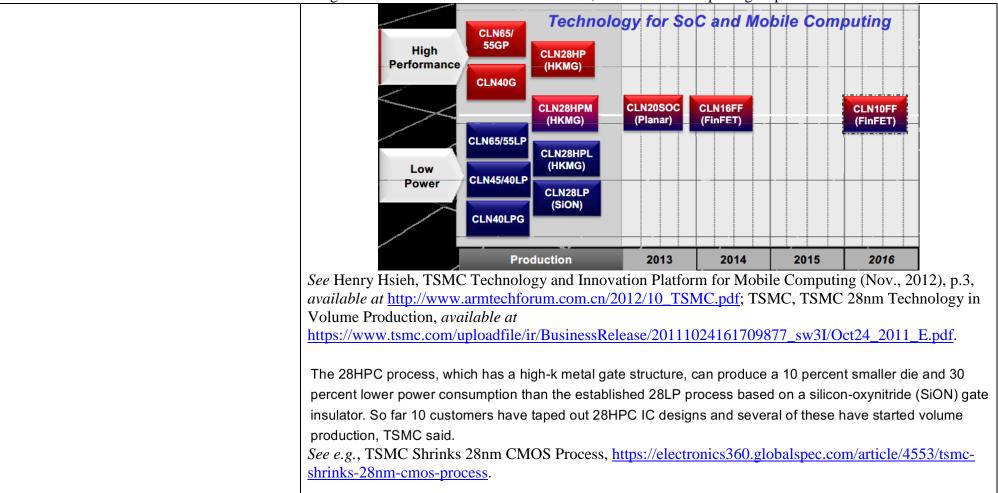

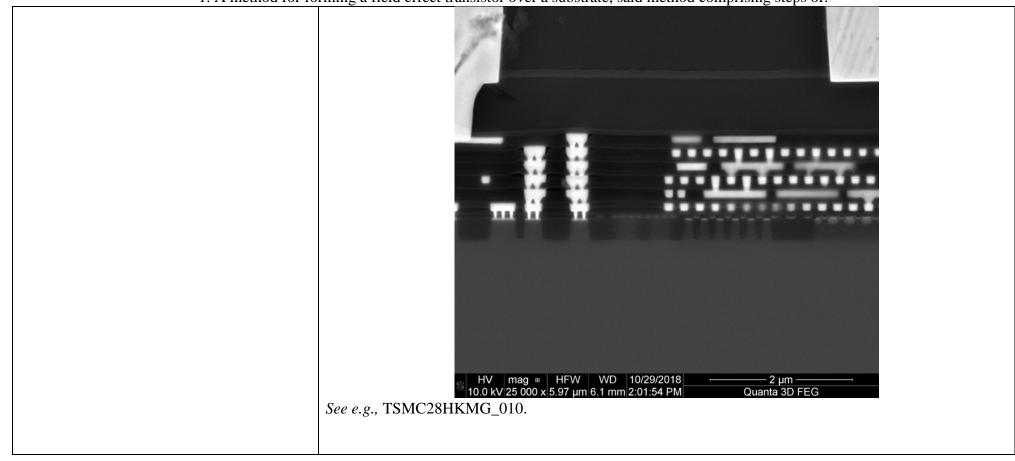

1. A method for forming a field effect Integrated circuits manufactured using TSMC's 20nm and 28nm High-K Metal Gate (HKMG) process node (the "TSMC Product") are manufactured using a method of forming a field effect transistor over a transistor over a substrate, said method comprising steps of: substrate. For example, the Mstar MSDURP1602 integrated circuit (the "Mstar Chip") is an exemplary TSMC Product. P1602-R-00AH ATOGV57A 1822A See e.g., TSMC28HKMG\_008. The Mstar Chip is manufactured using TSMC's 28nm HPC process node. Allwinner's octa-core A83 application processor is one of those fabricated in 28HPC. Amlogic's S812 4K HEVC modem, containing quad-core Cortex-A9 and T450 Mali GPU is another. MStar is using 28HPC for 4K ultrahigh definition television processor and Spreadtrum is offering smartphone ICs using the technology. See e.g., TSMC Shrinks 28nm CMOS Process, https://electronics360.globalspec.com/article/4553/tsmcshrinks-28nm-cmos-process. TSMC's high performance technology nodes, including HP, HPL, and HPM, and HPC use high-k metal gate (HKMG) gate-last technology.

#### Case 1:19-cv-00308-MN Document 1.8, Filed 97/12/19 Page 4 of 26 PageID #: 160

"1. A method for forming a field effect transistor over a substrate, said method comprising steps of:"

"1. A method for forming a field effect transistor over a substrate, said method comprising steps of:"

| 1. A method for forming a neid effect transistor over a substrate, said method comprising steps of. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                     | TSMC became the first foundry to provide the world's first 28nm General Purpose process<br>technology in 2011 and has been adding more options ever since. TSMC provides<br>customers with foundry's most comprehensive 28nm process portfolio that enable products<br>that deliver higher performance, save more energy savings, and are more eco-friendly.                                                                                                                                                                                    |  |  |

|                                                                                                     | TSMC's 28nm process technology features high performance and low power consumption<br>advantages plus seamless integration with its 28nm design ecosystem to enable faster time-<br>to-market. The 28nm process technology supports a wide range of applications, including<br>Central Processing Units (CPUs), graphic processors (GPUs), high-speed networking chips,<br>smart phones, application processors (APs), tablets, home entertainment, consumer<br>electronics, and the Internet of Things.                                        |  |  |

|                                                                                                     | TSMC's industry-leading 28nm process technology mainly uses High-k Metal Gate (HKMG) gate-last technology. Compared to the gate-first technology, the gate-last offering provides more advantages, including lower leakage current and better chip performance.<br>See e.g., TSMC, 28nm Technology,                                                                                                                                                                                                                                             |  |  |

|                                                                                                     | http://www.tsmc.com/english/dedicatedFoundry/technology/28nm.htm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                                                                                                     | TSMC Products share substantially similar structure, function, operation, and implementation with respect to the claims at issue. For example, the 20nm technology node is a die shrink of the 28nm HKMG technology node.                                                                                                                                                                                                                                                                                                                       |  |  |

|                                                                                                     | So now the first shoe has dropped (must check where that metaphor came from!), and we have a TSMC-<br>fabbed 20-nm part in-house. It is in the lab at the moment, and we are waiting for the analysis results.                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                                                                     | It will be interesting to see what changes TSMC has made from the 28-nm process; in general, I expect mostly a shrink of the latter process, with no change to the materials of the high-k stack, though maybe to the sequence. At 28-nm the high- k was put down first, before the dummy poly gate, and it makes sense to move that deposition to after poly gate removal. That way, the high-k layer does not have to suffer the poly formation and source-drain engineering process steps, saving it from quite a bit of thermal processing. |  |  |

|                                                                                                     | <i>See e.g.</i> , Semiconductor Manufacturing & Design Community, "TSMC 20nm Arrives – The First Shoe Drops," <u>https://semimd.com/chipworks/2014/07/21/tsmc-20nm-arrives-the-first-shoe-drops/.</u>                                                                                                                                                                                                                                                                                                                                           |  |  |

"1. A method for forming a field effect transistor over a substrate, said method comprising steps of:"

|                            | <b>NI</b> 1       | 20         | 20        |

|----------------------------|-------------------|------------|-----------|

|                            | Node              | 28         | 20        |

|                            | Transistor        | Planar     | Planar -  |

|                            | Туре              | – bulk     | bulk      |

|                            |                   |            |           |

|                            | Gate              | HKMG       | HKMG      |

|                            |                   |            |           |

|                            | Threshold         | 4          | 4         |

|                            | voltages          | -          |           |

|                            | voltages          |            |           |

|                            | Ci i              | DSL,       | DSL,      |

|                            | Strain            | eSiGe,     | eSiGe,    |

|                            |                   | SM         | SM        |

|                            |                   | 5171       | 5101      |

|                            | Metal             | 10         | 10        |

|                            | layers            |            |           |

|                            |                   |            |           |

|                            | DSL = Dual Stress | s Liner, S | 6M = Stre |

|                            | eSiGe = embedd    | ed Silico  | n Germa   |

| See e.g., IC Knowledge TSN | MC Structural Par | rameters   | ,         |

| https://www.semiwiki.com/  |                   |            |           |

| structure.pdf.             |                   |            |           |

| <u>suuciuic.pui.</u>       |                   |            |           |

| Foun                                                                                                                                                              | dry roadma                        | p examı                    | ole - TSN         | ЛС                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|-------------------|------------------------|

|                                                                                                                                                                   |                                   | 28nm                       | 20nm              |                        |

|                                                                                                                                                                   | Year                              | 2011                       | 2014              |                        |

|                                                                                                                                                                   | Transistor                        | Planar                     | Planar            |                        |

|                                                                                                                                                                   | Channel<br>(NMOS/PMOS)            | Si/Si                      | Si/Si             |                        |

|                                                                                                                                                                   | Threshold voltages                | 4                          | 4                 |                        |

|                                                                                                                                                                   | Metal layers                      | 10                         | 10                |                        |

|                                                                                                                                                                   | Contact and Via –<br>Interconnect | W –<br>Cu/Ta/TaN           | W –<br>Cu/Ta/TaN  |                        |

|                                                                                                                                                                   | Strain                            | DSL, eSiGe,<br>SM          | DSL,<br>eSiGe, SM |                        |

|                                                                                                                                                                   | CPP (nm)                          | 113                        | 90                |                        |

|                                                                                                                                                                   | MMP (nm)                          | 90                         | 64                |                        |

| See e.g., Technology and Cost Tr<br>https://www.icknowledge.com/ne<br>odes%20-%20Revised.pdf.<br>The TSMC Product comprises fie<br>Mstar Chip comprises FETs form | ews/Technology%2                  | 20and%20Co<br>s (FETs) for | ost%20Trend       | ds%20at%20Advanced%20N |

Case 1:19-cv-00308-MN Document 1. No. 5,199,97212/139 Page 8 of 26 PageID #: 164 "1. A method for forming a field effect transistor over a substrate, said method comprising steps of:"

#### Case 1:19-cv-00308-MN Document 1.8. Filed 97/12/19/19 Page 9 of 26 PageID #: 165

"forming an interfacial oxide layer over a channel region of said substrate, said interfacial oxide layer having a first thickness;"

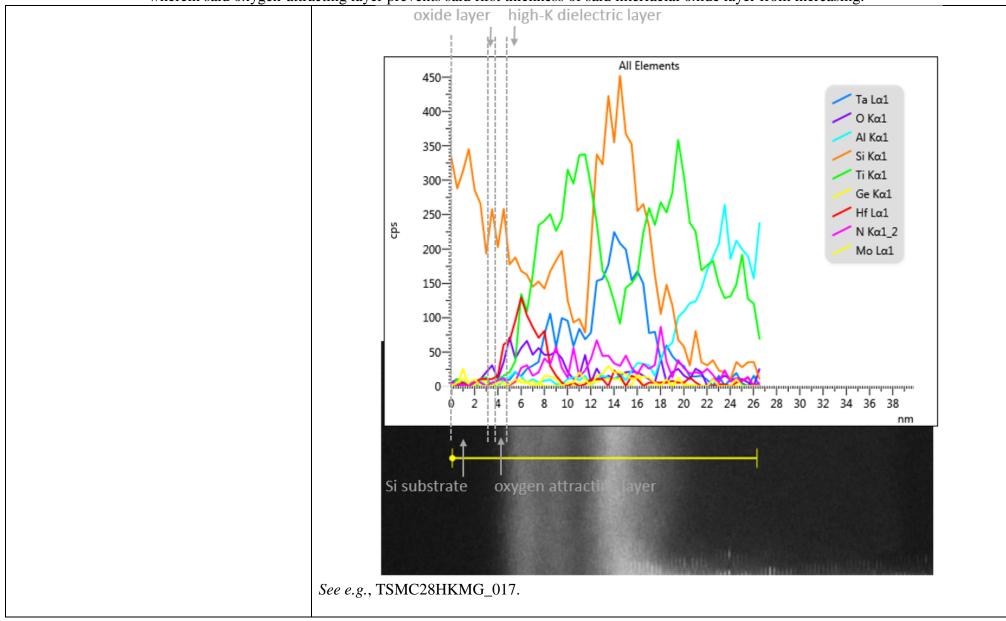

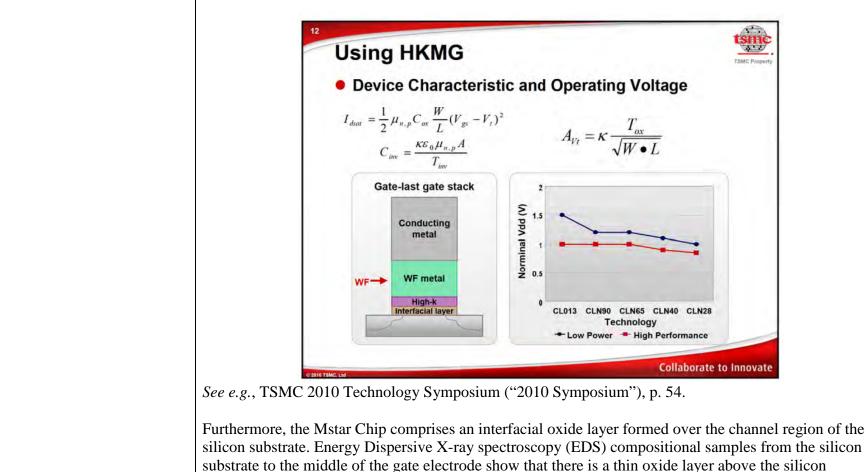

forming an interfacial oxide layer over a channel region of said substrate, said interfacial oxide layer having a first thickness; The TSMC Product is manufactured using the step of forming an interfacial oxide layer over a channel region of said substrate, said interfacial oxide layer having a first thickness.

For example, in the Mstar Chip, an interfacial layer is formed as shown below.

substrate.

"forming an interfacial oxide layer over a channel region of said substrate, said interfacial oxide layer having a first thickness;"

"forming an interfacial oxide layer over a channel region of said substrate, said interfacial oxide layer having a first thickness;"

"forming an interfacial oxide layer over a channel region of said substrate, said interfacial oxide layer having a first thickness;"

# Case 1:19-cv-00308-MN Docsment 1- No. Filed 02/13/19 Rage 13 of 26 PageID #: 169

"forming an oxygen-attracting layer over said interfacial oxide layer;"

| forming an oxygen autacung layer over sale interfactar oxide layer,   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

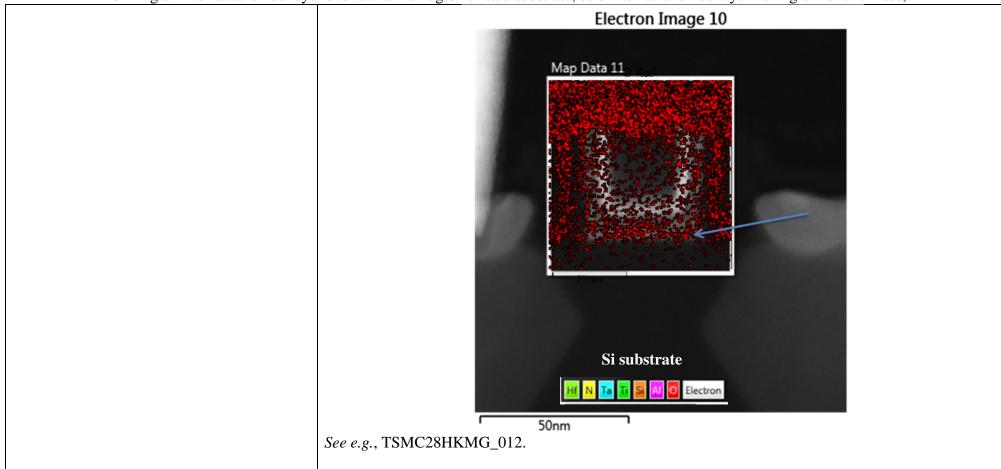

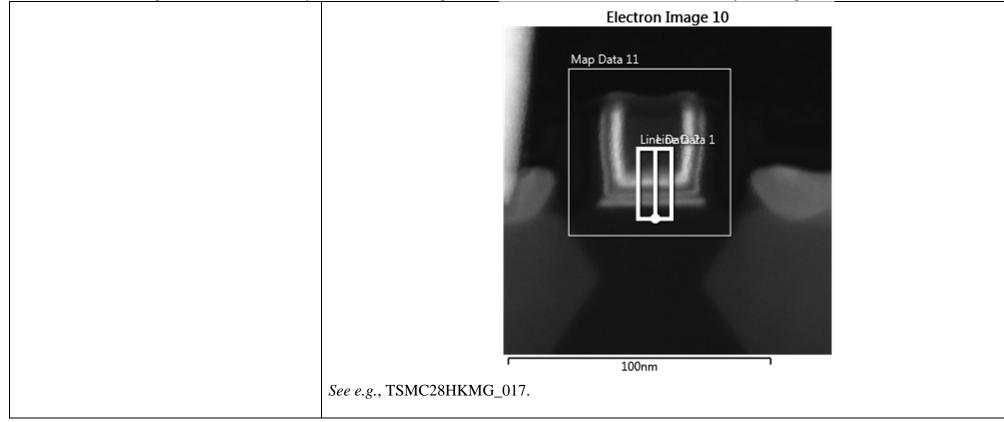

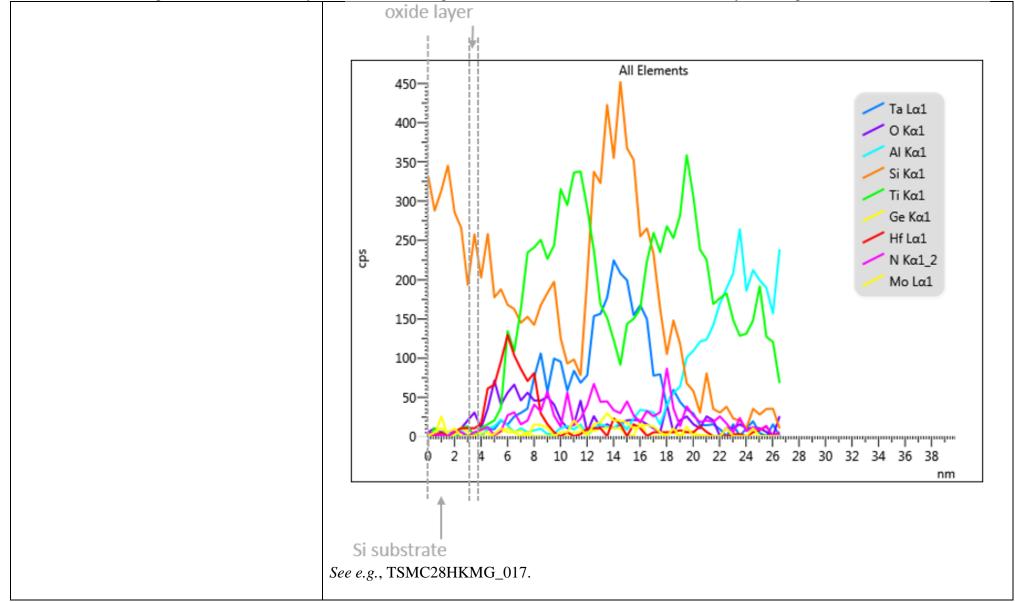

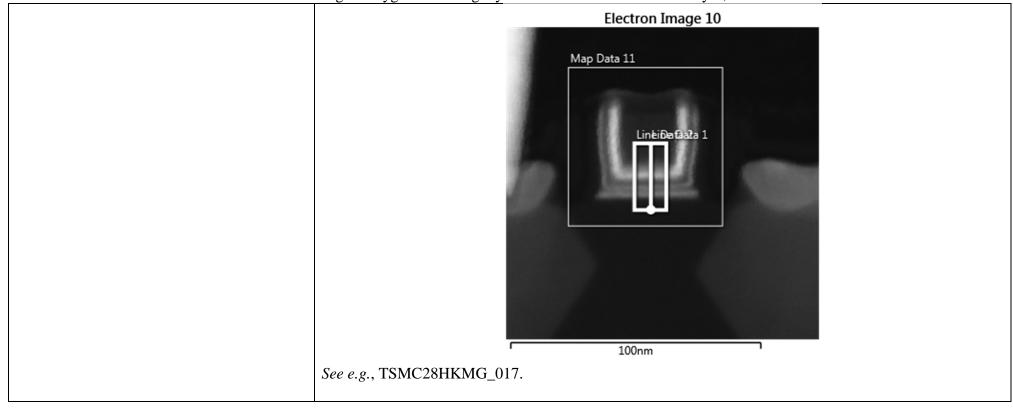

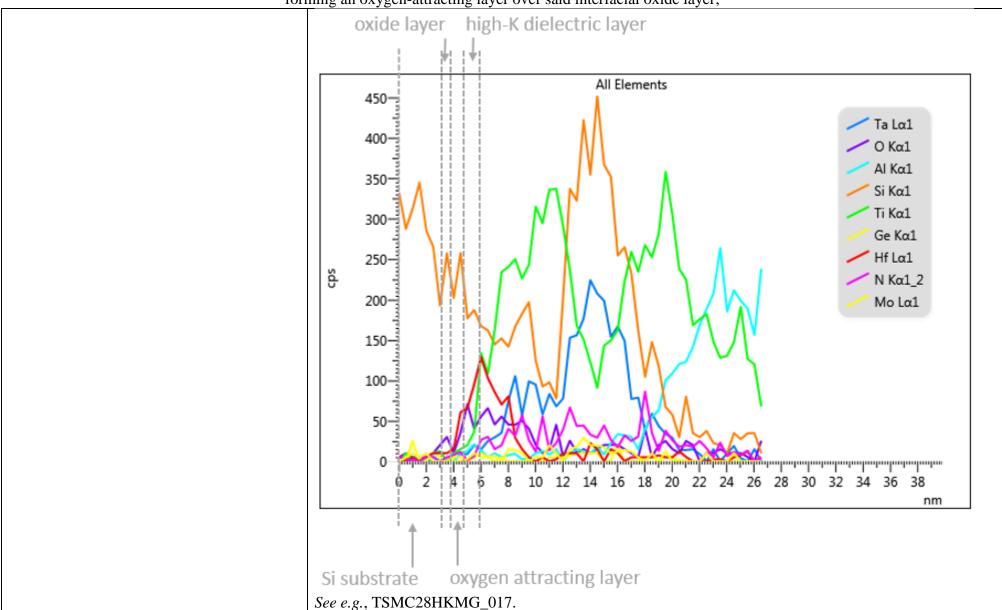

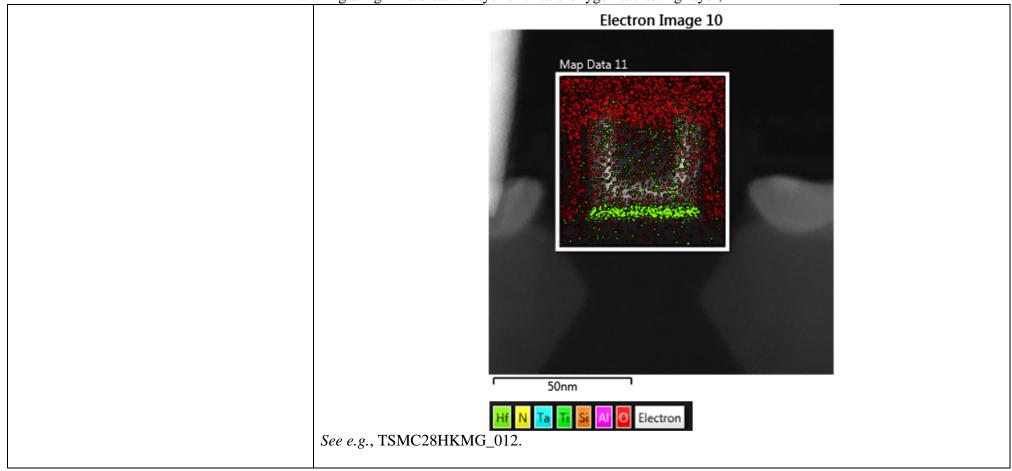

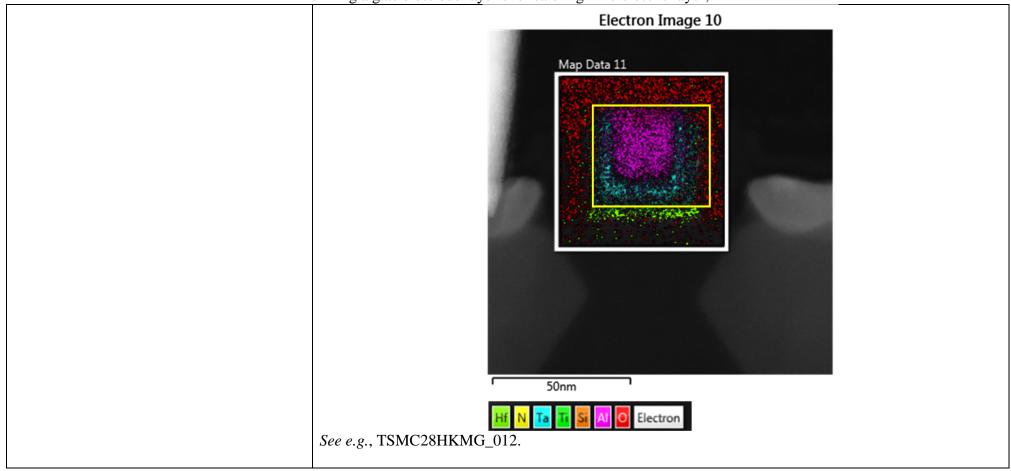

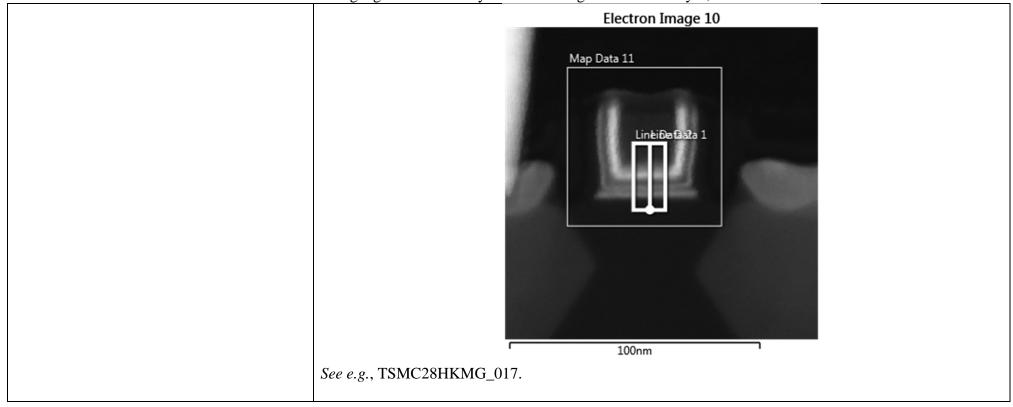

| forming an oxygen-attracting layer over said interfacial oxide layer; | The TSMC Product is manufactured using the step of forming an oxygen-attracting layer over the interfacial oxide layer.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

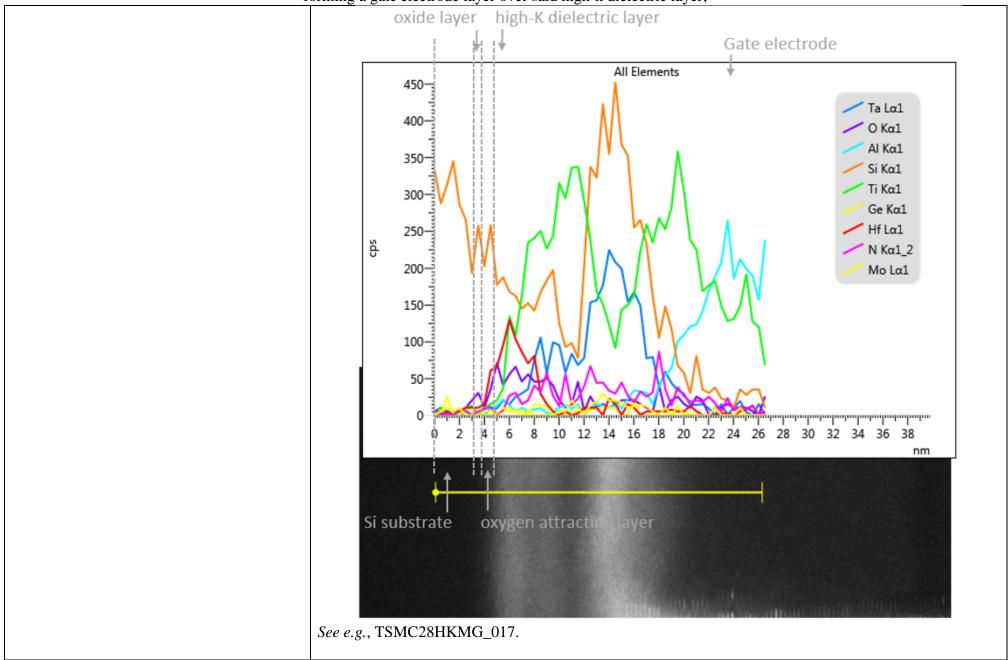

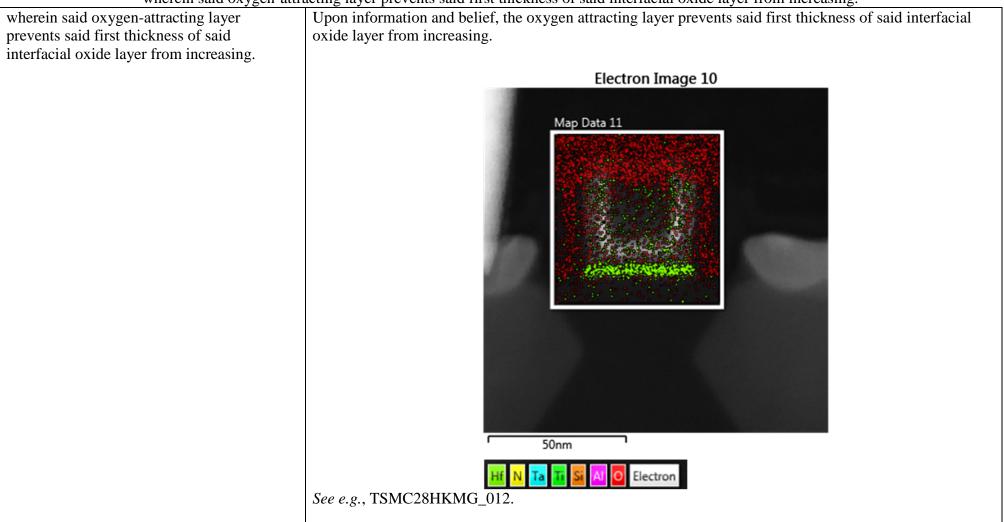

|                                                                       | For example, as shown below, the Mstar Chip contains a layer of Hafnium and Hafnium Oxide over the interfacial oxide layer. EDS compositional samples from the silicon substrate to the middle of the gate electrode show that there is a thin oxygen attracting layer between the oxide layer and the high-K dielectric layer. In particular, as illustrated below, the hafnium signal begins to rise near the oxygen attracting layer region and a local oxygen peak closely follows. |  |  |  |

|                                                                       | Electron Image 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                                                       | Map Data 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                                                                       | 50nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                                                       | See e.g., TSMC28HKMG_012.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

"forming an oxygen-attracting layer over said interfacial oxide layer;"

Case 1:19-cv-00308-MN Document 1-No. Filed 02/13/19m Page 15 of 26 PageID #: 171

"forming an oxygen-attracting layer over said interfacial oxide layer;"

#### Case 1:19-cv-00308-MN Document 1 No. Eiled 02/1:3/19m Page 16 of 26 PageID #: 172

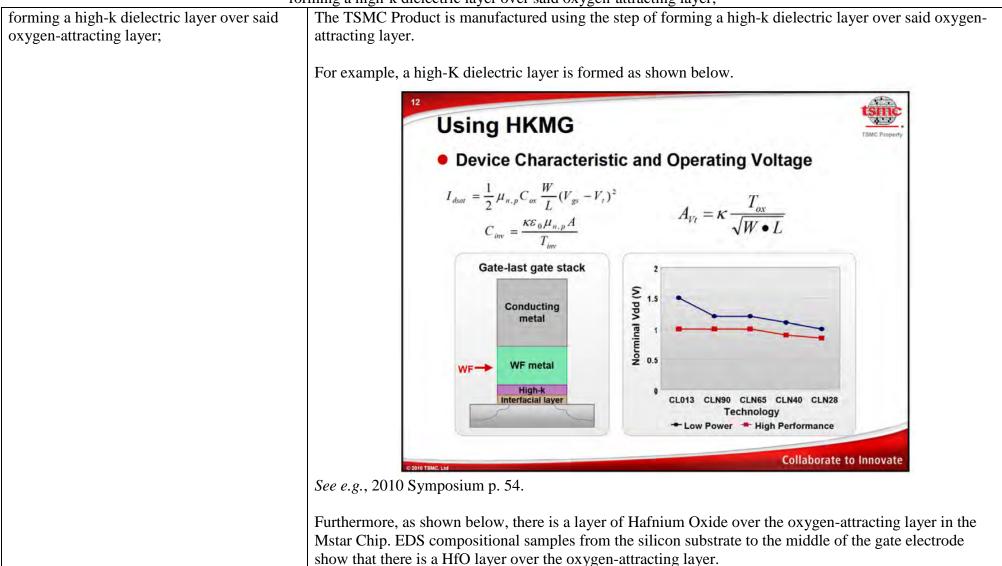

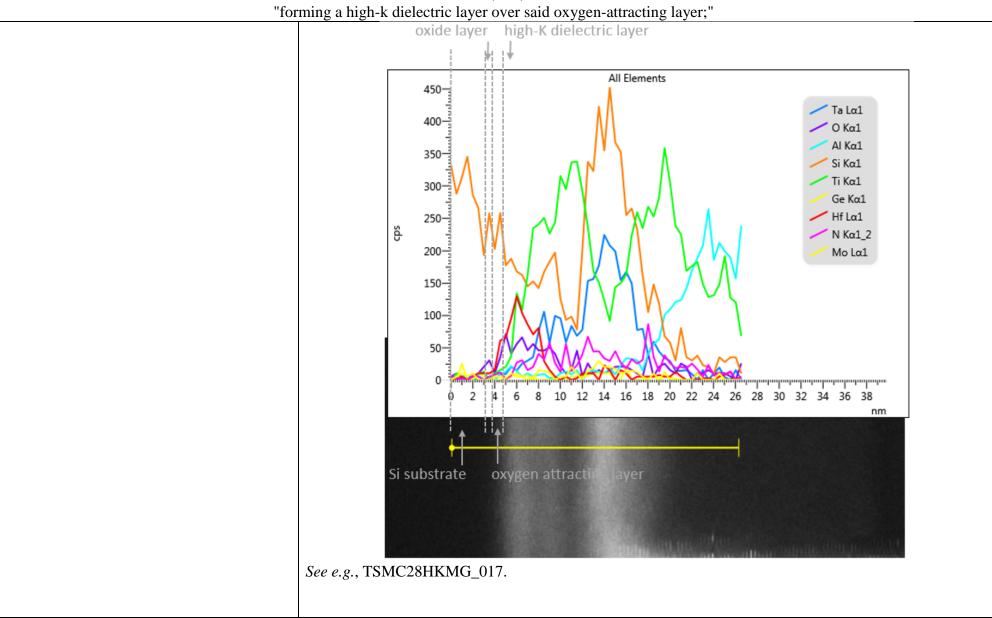

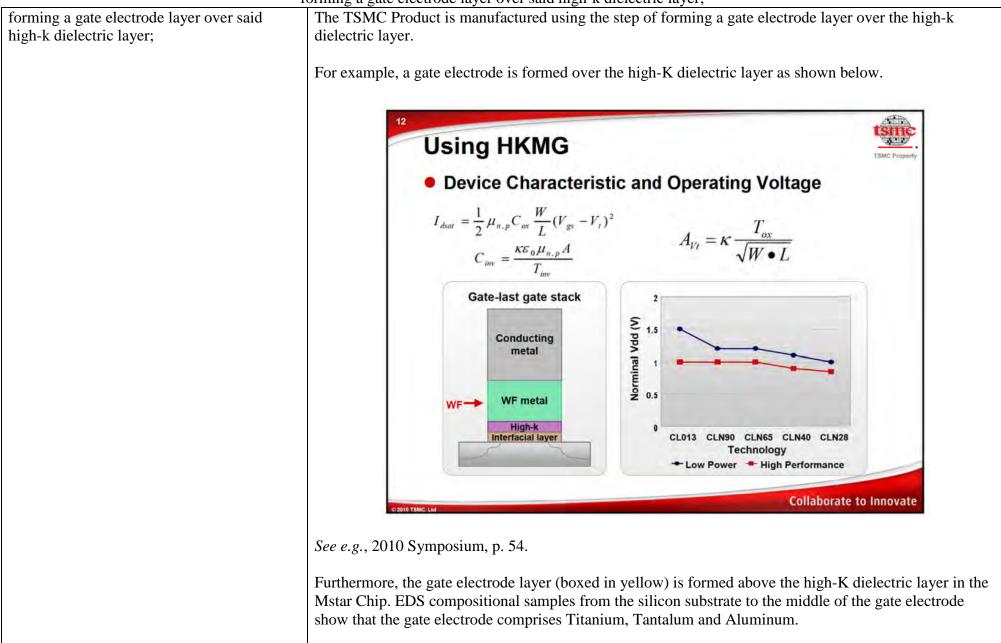

"forming a high-k dielectric layer over said oxygen-attracting layer;"

"forming a high-k dielectric layer over said oxygen-attracting layer;"

"forming a high-k dielectric layer over said oxygen-attracting layer;"

### Case 1:19-cv-00308-MN Docyment 1- No. Eilog 02/13/19m Page 19 of 26 PagelD #: 175

#### Case 1:19-cv-00308-MN Document 1 No. Filed 3/1:3/19m Page 20 of 26 PageID #: 176

## Case 1:19-cv-00308-MN Document 1 No. Filed 02/13/19 Rage 23 of 26 PageID #: 179

# Case 1:19-cv-00308-MN Document 1- No. Files 703/2:419 Page 24 of 26 PageID #: 180

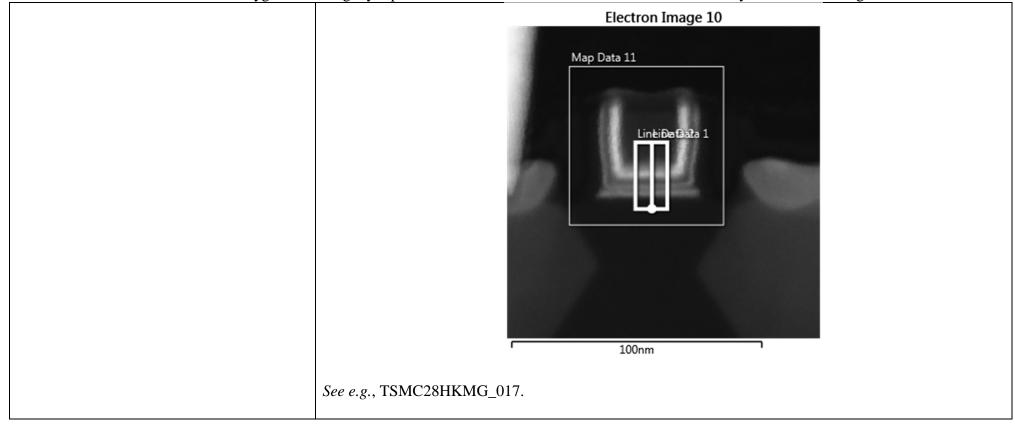

"wherein said oxygen-attracting layer prevents said first thickness of said interfacial oxide layer from increasing."

"wherein said oxygen-attracting layer prevents said first thickness of said interfacial oxide layer from increasing."

# Case 1:19-cv-00308-MN Document 1-90. Files 7,972.3 (19) Page 26 of 26 PageID #: 182

"wherein said oxygen-attracting layer prevents said first thickness of said interfacial oxide layer from increasing."